Verification & Proof:

Engineering You Can Trust

From automated verification to transparent proof points, our methods are trusted by

Tier-1 organizations building high-reliability systems.

What Makes Our Verification Trusted by Tier-1 Leaders

Built on evidence, validated in real systems.

Deterministic Workflows

Predictable verification outcomes maintained across environments, tools, and distributed teams.

Full Transparency

Clear traceability of test intent, execution results, and verification coverage.

Automation First

Configuration-driven verification flows improve consistency and reduce manual dependency.

Hardware + Software Proof

Validation extends from RTL through firmware, drivers, and full system behavior.

Verification Framework & Toolchain

Structured workflows with automated execution.

Planning

- Requirements mapping & traceability

- Modular testbench design

- Feature & verification planning

Environment

- UVM/OVM testbenches

- BFMs, monitors & scoreboards

- Reference models & golden vectors

Execution

- Directed & constrained-random tests

- Assertion-based functional checks

- FPGA/hardware prototyping

Measurement

- Functional & code coverage

- Latency & throughput metrics

- Error injection & performance logs

Toolchain

- Questa, VCS, Xcelium simulators

- Verilator for open-source flows

- Jenkins/GitLab CI automation

- Python & YAML scripts

Continuous Integration & Deployment: Reliable and Traceable

Each commit activates end-to-end verification, from code linting to coverage reporting.

CI/CD Pipeline Stages

Sidebar block — YAML-Driven Automation

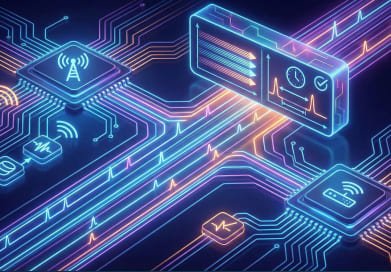

Architecture Overview

High-level architectural overview of Logic Fruit’s programmable system design

High-Speed Interconnects

- PCIe Gen5/6/7 VIP

- AXI/AXI-Stream VIP

- AXI/AXI-Stream VIP

Video & Sensor Interfaces

- ARINC 818 Analyzer

- ARINC 818 Generator

- Multi-Format Video Generators

- DVI/STANAG Converters (tester logic reused from A-3.1.3)

RF & JESD

- JESD204B/C VIP

- Lane Alignment monitors

- Deterministic latency checkers

Networking

- UDPa/TCP generators

- 10G/40G/100G MAC VIP

- Packet load/traffic generators

Proven in Real-World Systems

Our verification is proven by flawless operation in production environments.

Metrics Bar

- 0 Critical Bugs post-deployment (for multiple Tier-1 programs).

- 100% Traceability between requirements ↔ tests

- 95–98% Functional Coverage across large programs

Case Highlights

- Global Data Center OEM — Verified PCIe subsystem for high-throughput NIC platform.

- Aerospace Avionics Supplier — ARINC 818 display pipelines validated with our testbench & analyzer suite

- 5G/Telecom Vendor — Verified JESD204C RF front-end processing system

Short Testimonials

Aniruddha Venu

Lorem Ipsum is simply dummy text of the printing and typesetting industry. Lorem Ipsum has been the industry's standard dummy text ever since the 1500s

Siva Subramaniam

Lorem Ipsum is simply dummy text of the printing and typesetting industry. Lorem Ipsum has been the industry's standard dummy text ever since the 1500s

Sham Dahibhavkar

Lorem Ipsum is simply dummy text of the printing and typesetting industry. Lorem Ipsum has been the industry's standard dummy text ever since the 1500s

Siva Subramaniam

Lorem Ipsum is simply dummy text of the printing and typesetting industry. Lorem Ipsum has been the industry's standard dummy text ever since the 1500s

Standards & Certification

Structured quality practices that meet certification standards.

Quality Systems & Documentation

- DO-254-compliant flows

- ISO-style requirement & change control

- Architecture, test plans & logs

Standards & Framework Alignment

- PCIe (PCI-SIG)

- VESA display protocols

- MIPI (optional)

- Ethernet/UDP (IEEE)

- UVM verification frameworks

Proof Artifacts Provided to Customers

- Verification plans

- Coverage reports

- Error/stress logs

- Compliance logs

- Release notes

Build High-Performance FPGA & SoC Systems With Confidence

our verification experts today.