System Platforms

Modular Hardware Platforms for High-Performance Systems

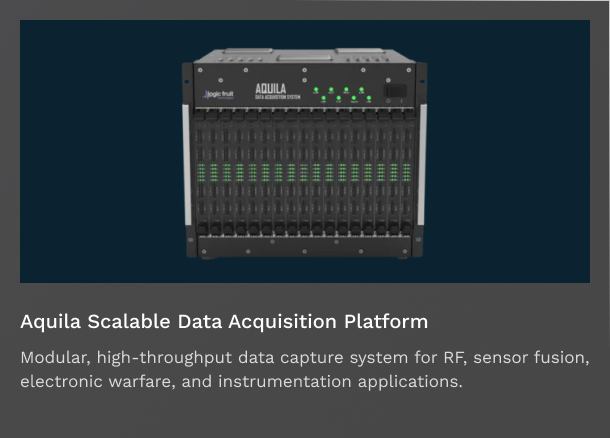

Reconfigurable platforms built for data acquisition, protocol testing, high-speed recording, and intelligent compute acceleration.

Our system platforms accelerate prototyping and deployment across aerospace, industrial automation, telecom, autonomous systems, and semiconductor validation. Each platform is engineered for rugged performance, low-latency data movement, and seamless integration with our interface/IP ecosystem.

KEY SPECS

Engineering-Ready Specifications

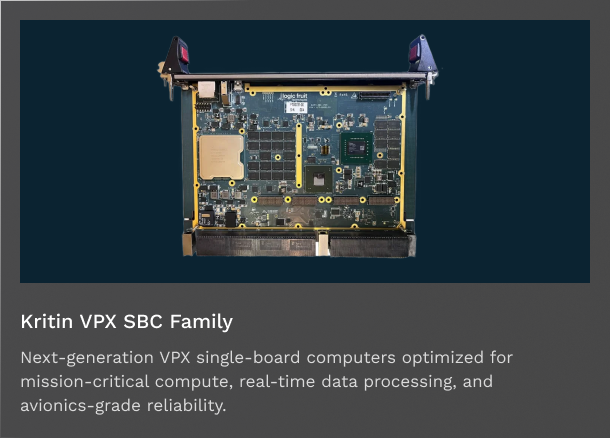

Kritin VPX SBC Family

- 6U/3U VPX configurations

- High-performance SoC/FPGA compute

- Rugged MIL standards

- Multi-display, avionics bus, and high-speed I/O support

Video & Sensor Interfaces

- ARINC 818 Analyzer

- ARINC 818 Generator

- Multi-format video generators

- DVI/STANAG converters (tester logic reused from A-3.1.3)

RF & JESD

- JESD204B/C/D VIP

- Lane alignment monitors

- Deterministic latency checkers

Networking

- UDPa/TCP generators

- 10G/40G/100G MAC VIP

- Packet load/traffic generators

SLAs & SUPPORT

Enterprise-Grade Commitments & Support

Guaranteed Response & Resolution Windows

- Engineering response within agreed SLA

- Dedicated Slack/Teams channel (optional)

- Critical-path issue escalation within 24 hours

Maintenance & Feature Updates

- Bug fixes included for licensed versions

- Performance tuning for new silicon revisions

- Optional: Custom IP improvements & roadmap

Hands-On Bring-Up Assistance

- Remote or on-site

bring-up - Integration workshops with system architects

- Post-handover support for regression and certification

Hands-On Bring-Up Assistance

- Remote or on-site

bring-up - Integration workshops with system architects

- Post-handover support for regression and certification

Logic Fruit offers modular and transparent licensing terms for PCIe/CXL IP, interface subsystems, and system platforms. Whether you’re building FPGA-based accelerators, validating silicon, or deploying high-performance systems, you can adopt our technology through a model that fits your engineering and commercial needs.

Kritin VPX SBC Family

- 6U/3U VPX configurations

- High-performance SoC/FPGA compute

- Rugged MIL standards

- Multi-display, avionics bus, and high-speed I/O support

Video & Sensor Interfaces

- ARINC 818 Analyzer

- ARINC 818 Generator

- Multi-format video generators

- DVI/STANAG converters (tester logic reused from A-3.1.3)

RF & JESD

- JESD204B/C/D VIP

- Lane alignment monitors

- Deterministic latency checkers

Networking

- UDPa/TCP generators

- 10G/40G/100G MAC VIP

- Packet load/traffic generators

Build High-Performance FPGA & SoC Systems With Confidence

Our engineering team can architect, partition, and optimize your next-generation compute or connectivity platform.

Board Support Packages (BSPs)

- Linux/RTOS support

- Device-tree, bootloaders, and peripheral bring-up

- PCIe drivers + DMA engines (where relevant)

Reference Designs

- JESD204 pipeline examples

- PCIe streaming reference

- Video and display reference stacks

- Sensor/DAQ examples for Aquila

Test & Validation Tools

- Loopback and functional test suites

- Interoperability test scripts

- Protocol analyzers (ARINC, JESD, UDP)

- Throughput/latency evaluation tools

Documentation & Training

- Architecture guides

- Schematic and layout notes

- Timing closure guidelines

- Setup workshops (optional)

APPLICATION MAPPING

Where These Platforms Are Used

| Platform | Aerospace & Mission Systems | Telecom & 5G/6G Infrastructure | Edge AI & Industrial Automation | Robotics & Autonomous Systems | Semiconductor Validation & Testing |

|---|---|---|---|---|---|

| Kritin VPX SBC | — | ||||

| Aquila Data Acquisition | |||||

| HDRR Recorder | — | — | |||

| Avant G70 PCIe Mini Board | — |

CERTIFICATIONS & ENGINEERING PRACTICES

Aligned to Global Aerospace Standards

Every licensed IP or subsystem is delivered with clear, engineering-grade verification evidence. eports are produced through our internal CI-based automation framework and validated using industry-standard compliance suites.

Latency Benchmarks

End-to-end latency measurements under varying payloads, workloads, and PCIe/CXL link widths.

Throughput Performance

Sustained and peak throughput numbers for JESD, PCIe, ARINC, Ethernet subsystems — on real hardware.

Coverage & Stress Testing

Functional coverage, directed/constraint-random scenarios, corner-case matrices, and error-injection tests.

Standards Compliance Evidence

Conformance test results for PCIe Base Spec, CXL, JESD204B/C/D, ARINC 818, and Ethernet.

Latency Benchmarks

End-to-end latency measurements under varying payloads, workloads, and PCIe/CXL link widths.

Standards Compliance Evidence

Conformance test results for PCIe Base Spec, CXL, JESD204B/C/D, ARINC 818, and Ethernet.

Standards Compliance Evidence

Conformance test results for PCIe Base Spec, CXL, JESD204B/C/D, ARINC 818, and Ethernet.

Coverage & Stress Testing

Functional coverage, directed/constraint-random scenarios, corner-case matrices, and error-injection tests.

Build High-Performance FPGA & SoC Systems With Confidence

Our engineering team can architect, partition, and optimize your next-generation compute or connectivity platform.